- 您现在的位置:买卖IC网 > Sheet目录1252 > VR1005CCA270-T (Taiyo Yuden)VARISTOR 27V 15PF 0402 SMD

�� �

�

�

�■� PRECAUTIONS�

�Precautions� on� the� use� of� Multilayer� chip� varistors.�

�1.� Circuit� Design�

�◆� Veri?cation� of� operating� environment,� electrical� rating� and� performance�

�1.� A� malfunction� in� medical� equipment,� spacecraft,� nuclear� reactors,� etc.� may� cause� serious� harm� to� human� life� or� have� severe� social� rami?cations.� As� such,�

�any� varistors� to� be� used� in� such� equipment� may� require� higher� safety� and/or� reliability� considerations� and� should� be� clearly� differentiated� from� components�

�Precautions�

�used� in� general� purpose� applications.�

�◆� Operating� Voltage� (Veri?cation� of� Rated� voltage)�

�1.� The� operating� voltage� for� varistors� must� always� be� lower� than� their� rated� values.�

�If� an� AC� voltage� is� loaded� on� a� DC� voltage,� the� sum� of� the� two� peak� voltages� should� be� lower� than� the� rated� value� of� the� varistor� chosen.� For� a� circuit� where�

�both� an� AC� and� a� pulse� voltage� may� be� present,� the� sum� of� their� peak� voltages� should� also� be� lower� than� the� varistor's� rated� voltage.�

�2.� PCB� Design�

�◆� Pattern� con?gurations� (Design� of� Land-patterns)�

�1.� When� varistors� are� mounted� on� a� PCB,� the� amount� of� solder� used� (size� of� ?llet)� can� directly� affect� varistor� performance.�

�Therefore,� the� following� items� must� be� carefully� considered� in� the� design� of� solder� land� patterns� :�

�(� 1� )� The� amount� of� solder� applied� can� affect� the� ability� of� chips� to� withstand� mechanical� stresses� which� may� lead� to� breaking� or� cracking.� Therefore,� when�

�designing� land-patterns� it� is� necessary� to� consider� the� appropriate� size� and� con?guration� of� the� solder� pads� which� in� turn� determines� the� amount� of�

�Precautions�

�solder� necessary� to� form� the� ?llets.�

�(� 2� )� When� more� than� one� part� is� jointly� soldered� onto� the� same� land� or� pad,� the� pad� must� be� designed� so� that� each� component's� soldering� point� is� separated�

�by� solder-resist.�

�◆� Pattern� con?gurations� (varistor� layout� on� panelized� [breakaway]� PC� boards)�

�1.� After� varistors� have� been� mounted� on� the� boards,� chips� can� be� subjected� to� mechanical� stresses� in� subsequent� manufacturing� processes� (PCB� cutting,�

�board� inspection,� mounting� of� additional� parts,� assembly� into� the� chassis,� wave� soldering� the� re?ow� soldered� boards� etc).� For� this� reason,� planning� pattern�

�con?gurations� and� the� position� of� SMD� varistors� should� be� carefully� performed� to� minimize� stress.�

�◆� Pattern� con?gurations� (Design� of� Land-patterns)�

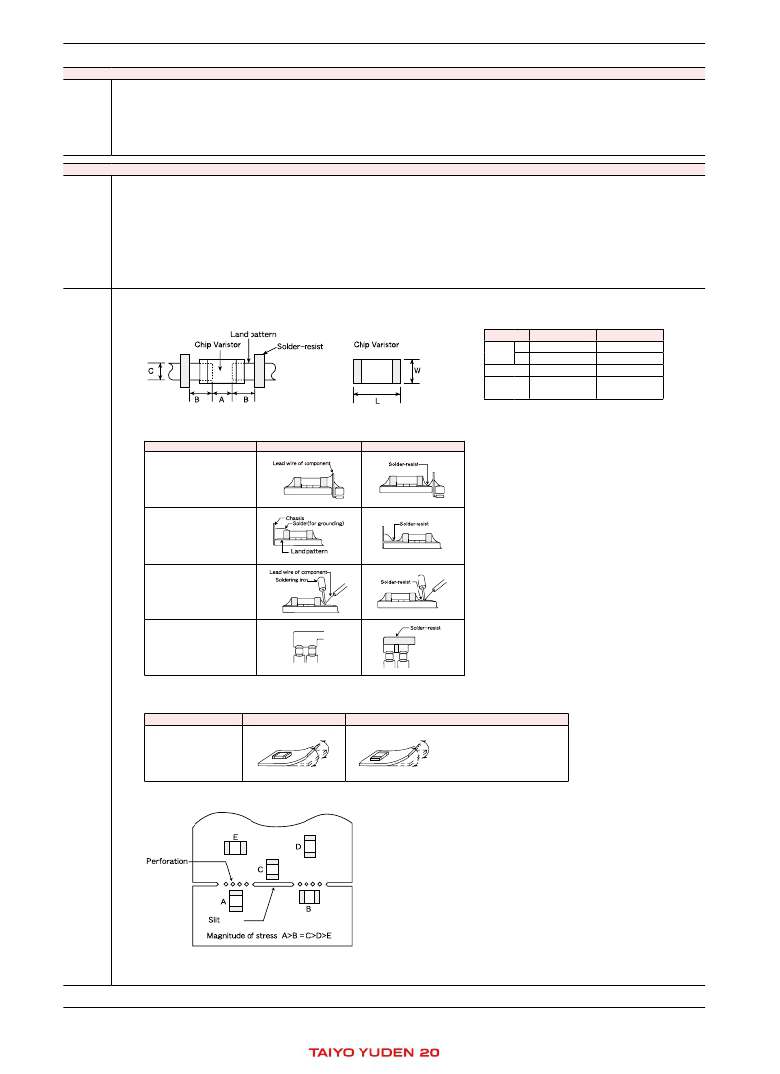

�1.� The� following� diagrams� and� tables� show� some� examples� of� recommended� patterns� to� prevent� excessive� solder� amounts.� (larger� ?llets� which� extend� above�

�the� component� end� terminations)� Examples� of� improper� pattern� designs� are� also� shown.�

�(� 1� )� Recommended� land� dimensions� for� a� typical� chip� varistor� land� patterns� for� PCBs�

�Recommended� land� dimensions� for� re?ow-soldering�

�Type�

�063�

�1005,� 105C�

�Size�

�A�

�B�

�C�

�L�

�W�

�0.6�

�0.3�

�0.2� ~� 0.30�

�0.2� ~� 0.30�

�0.25� ~� 0.40�

�1.0�

�0.5�

�0.45� ~� 0.55�

�0.40� ~� 0.50�

�0.45� ~� 0.55�

�Unit� :� mm�

�Excess� solder� can� affect� the� ability� of� chips� to� withstand� mechanical� stresses.� Therefore,� please� take� proper� precautions� when� designing� land-patterns.�

�(� 2� )� Examples� of� good� and� bad� solder� application�

�Technical�

�consider-�

�ations�

�Items�

�Mixed� mounting� of� SMD�

�and� leaded� components�

�Component� placement�

�close� to� the� chassis�

�Hand-soldering� of� leaded�

�components� near� mounted�

�components�

�Horizontal� component�

�placement�

�Not� recommended�

�Recommended�

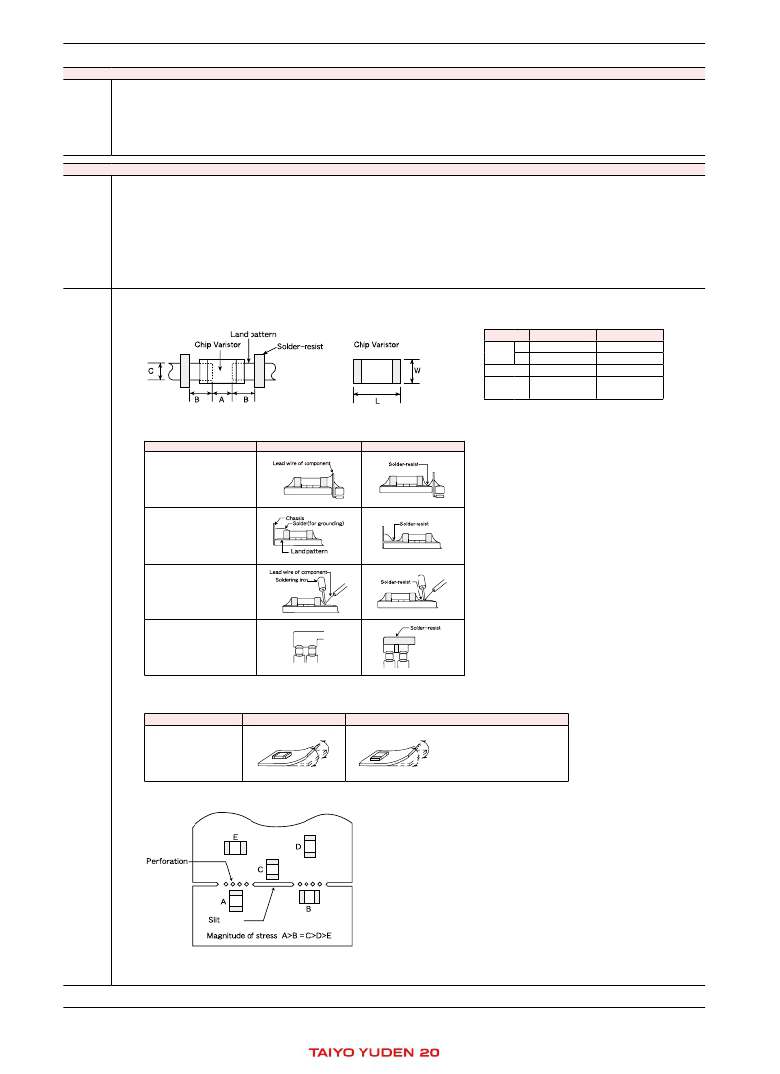

�◆� Pattern� con?gurations� (varistor� layout� on� panelized� [breakaway]� PC� boards)�

�1-1.� The� following� are� examples� of� good� and� bad� varistor� layout;� SMD� varistors� should� be� located� to� minimize� any� possible� mechanical� stresses� from� board� warp�

�or� de?ection.�

�De?ection� of� the� board�

�Not� recommended�

�Recommended�

�Position� the� component�

�at� a� right� angle� to� the� direction�

�of� the� mechanical� stresses� that�

�are� anticipated.�

�1-2.� To� layout� the� varistors� for� the� breakaway� PC� board,� it� should� be� noted� that� the� amount� of� mechanical� stresses� given� will� vary� depending� on� varistor� layout.�

�The� example� below� shows� recommendations� for� better� design.�

�1-3.� When� breaking� PC� boards� along� their� perforations,� the� amount� of� mechanical� stress� on� the� varistors� can� vary� according� to� the� method� used.� The� following�

�methods� are� listed� in� order� from� least� stressful� to� most� stressful:� push-back,� slit,� V-grooving,� and� perforation.� Thus,� any� ideal� SMD� varistor� layout� must� also�

�consider� the� PCB� splitting� procedure.�

�*� This� catalog� contains� the� typical� speci� ?cation� only� due� to� the� limitation� of� space.� When� you� consider� the� purchase� of� our� products,� please� check� our� speci� ?cation.�

�For� details� of� each� product� (characteristics� graph,� reliability� information,� precautions� for� use,� and� so� on),� see� our� Web� site� (http://www.ty-top.com/)� or� CD� catalogs.�

�chipv0102_reli-PRP4�

�12�

�chipv0102_reli_e-01�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

VR15AT18A650R

VARISTOR 18VDC 30A 150C RAD

VS230A

GAS TUBE GDT 230V AXIAL TR

VSHLD-EMR

VINCO ETHERNET MP3 RTC SHIELD

VSUPEV2

BOARD EVAL FOR MCP4022,4023,4024

VSUPEV

BOARD EVAL VOLT SUPERVISOR SOT23

VTERB-BLK-X2-UT4

LICENSE VITERBI DECODER XP2

VTERB-DECO-XP-N1

IP CORE VITERBI DECODER XPGA

VTP110F

POLYSWITCH PTC RESET 1.1A STRAP

相关代理商/技术参数

VR1005DDA080-T

制造商:TAIYO YUDEN 功能描述:Cut Tape 制造商:Taiyo Yuden 功能描述:0

VR100B080CU-2C

功能描述:DC/DC转换器 VRM10VID 1U 80A 12V to 0.8375-1.60V RoHS:否 制造商:Murata 产品: 输出功率: 输入电压范围:3.6 V to 5.5 V 输入电压(标称): 输出端数量:1 输出电压(通道 1):3.3 V 输出电流(通道 1):600 mA 输出电压(通道 2): 输出电流(通道 2): 安装风格:SMD/SMT 封装 / 箱体尺寸:

VR101

制造商:Fluke Electronics 功能描述:RECORDER VOLTAGE EVENT

VR101/001

制造商:Fluke Electronics 功能描述:RECORDER GERMAN VER FLUKE VR101/001

VR101/003

功能描述:数据记录与采集 VOLTAGE EVENT RECO

RoHS:否 制造商:Lantronix 描述/功能:Analog device server 显示器类型:None 电流额定值:

VR101/004

制造商:Fluke Electronics 功能描述:Additional VR101 voltage event recorder

VR101S

制造商:Fluke Electronics 功能描述:RECORDER VOLTAGE EVENT

VR101S/003

功能描述:数据记录与采集 VOLTAGE EVENT RECO

RoHS:否 制造商:Lantronix 描述/功能:Analog device server 显示器类型:None 电流额定值: